デジタル回路

| Jeans & Development | 電子ブロック工房 | 三日坊主 | フロントページ |

NMOSで作った、ジョンソンカウンター [デジタル回路]

2015年5月25日

MOSFET-Nを53個用いて、3つのFFを持つジョンソンカウンターを作成した。現在作成中のトランジスターCPUのクロックシグナルを制御する、大元になる部分の回路。

トランジスターを用いた回路設計がうまく行っているように思えるので、CPUの回路全体を近々公開しようかな。

トランジスターを用いた回路設計がうまく行っているように思えるので、CPUの回路全体を近々公開しようかな。

NMOSで作ったD-FF [デジタル回路]

2015年5月2日

コンピューターの原理を考える上で、フリップフロップ(FF)の理解は欠かせない。FFの安定動作は、CPU全体の安定動作に必須の条件だ。トランジスターでどの様に回路を組めば、FFが安定して動作するかを考察・実験してみた。

ほぼ出来上がっているトランジスターCPUの回路に於いて、FFはすべて、DタイプFFとして実装している。そこで、D-FFをブレッドボード上に構築して、予想したとおり動作するかどうかを、実験した。

ほぼ出来上がっているトランジスターCPUの回路に於いて、FFはすべて、DタイプFFとして実装している。そこで、D-FFをブレッドボード上に構築して、予想したとおり動作するかどうかを、実験した。

タイミング回路、再び [デジタル回路]

2009年7月23日

8 bit CPU への移行に伴って、クロック周りの回路を大幅に書き換えた。

まずできたのは、<%media(20090724-clock4.zip|以下のもの)%>。

まずできたのは、<%media(20090724-clock4.zip|以下のもの)%>。

クロック周り3 [デジタル回路]

2007年7月23日

ip++信号を、Prep4Read 信号近くに作成した。

ここで、問題が発覚。ipレジスタのやり取りをするジャンプ系命令の実行の際、上記のip++信号が下がるときと、命令実行信号の立ち上がり(ipレジスタへの代入をトリガー)が同じタイミングで起こる。ICの性質によっては、2回のトリガーが重なって、1回だけのトリガーになってしまう可能性がある。ip++ のあと、一呼吸してから ip 代入命令を実行すればよいのであるが、もともとジャンプ系の命令はすべてダブルクロックで実行されるので、この辺りの設計を変えなければならない。

そこで、ダブルクロック命令の実行の際は、1回休んでから命令の実行を開始することにした。したがって、ダブルクロック命令の実行には、3クロック消費されることになる。

ここで、問題が発覚。ipレジスタのやり取りをするジャンプ系命令の実行の際、上記のip++信号が下がるときと、命令実行信号の立ち上がり(ipレジスタへの代入をトリガー)が同じタイミングで起こる。ICの性質によっては、2回のトリガーが重なって、1回だけのトリガーになってしまう可能性がある。ip++ のあと、一呼吸してから ip 代入命令を実行すればよいのであるが、もともとジャンプ系の命令はすべてダブルクロックで実行されるので、この辺りの設計を変えなければならない。

そこで、ダブルクロック命令の実行の際は、1回休んでから命令の実行を開始することにした。したがって、ダブルクロック命令の実行には、3クロック消費されることになる。

クロック周り2 [デジタル回路]

2007年7月23日

目的に合うように、先日のクロック周りの回路をさらに拡張していくうちに、スパゲッティの様な回路になってしまった。もしかしたらうまく働くのかもしれないが、おそらく誤作動するだろう。

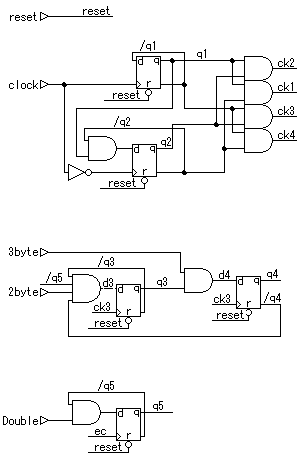

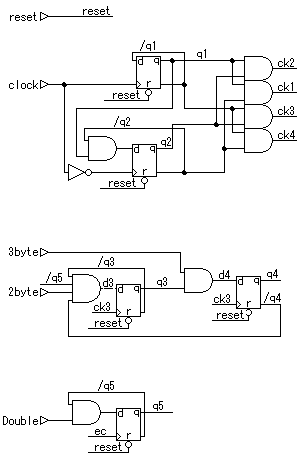

源内CADの使い方にも慣れてきたので、一から作り直すことにした。今回の回路は、systematic に仕上がっているので、拡張性が高くバグの混入の可能性も低いと思われる。新しいタイミング回路のメイン部分は次のとおり。

上の回路は、水晶発信からのシグナルを4つのクロックに分解する部分。2つ目のFFのデータ入力部に、AND回路を入れた。これを入れなかった前の回路は、リセットスイッチを押したときの水晶発信からのクロックが1か0かによって、誤作動する可能性があった。

真ん中と下の回路は、それぞれ、2バイト・3バイト命令の制御と、1つの命令で2回のクロックが必要な場合の制御。シンプルな回路に収まった(ラインecは、命令実行トリガー;記事の続きを参照)。

源内CADの使い方にも慣れてきたので、一から作り直すことにした。今回の回路は、systematic に仕上がっているので、拡張性が高くバグの混入の可能性も低いと思われる。新しいタイミング回路のメイン部分は次のとおり。

上の回路は、水晶発信からのシグナルを4つのクロックに分解する部分。2つ目のFFのデータ入力部に、AND回路を入れた。これを入れなかった前の回路は、リセットスイッチを押したときの水晶発信からのクロックが1か0かによって、誤作動する可能性があった。

真ん中と下の回路は、それぞれ、2バイト・3バイト命令の制御と、1つの命令で2回のクロックが必要な場合の制御。シンプルな回路に収まった(ラインecは、命令実行トリガー;記事の続きを参照)。