デジタル回路

| Jeans & Development | 電子ブロック工房 | 三日坊主 | フロントページ |

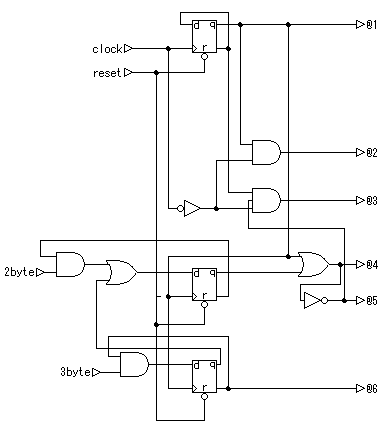

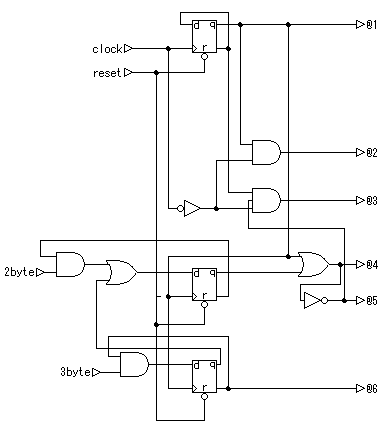

クロック周り [デジタル回路]

2007年7月19日

クロック周りの回路は、こんな感じで。

タイミングが難しいので、源内CADを用いて回路図を作成し、シミュレーションを行いながら回路図を完成させた。なお、この回路図の完成により、2バイト命令・3バイト命令を実現できることが分かったので、CPUの機能はこれに従って変更していくことになる。

タイミングが難しいので、源内CADを用いて回路図を作成し、シミュレーションを行いながら回路図を完成させた。なお、この回路図の完成により、2バイト命令・3バイト命令を実現できることが分かったので、CPUの機能はこれに従って変更していくことになる。

8ビット演算回路 [デジタル回路]

2007年6月29日

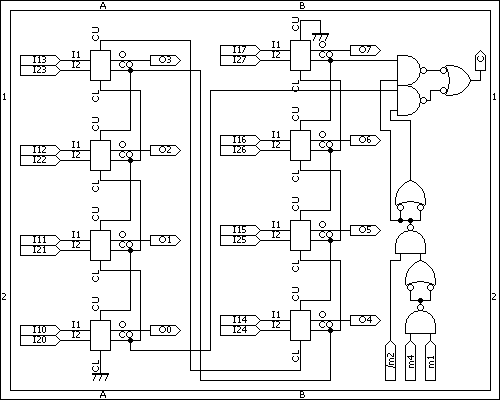

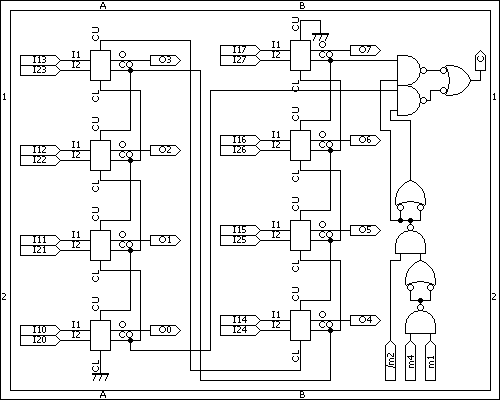

先日の回路を組み合わせて、8ビットどうしの演算をするための回路を設計した。実行できるのは、加算・減算・NAND・NOR・右シフト・左シフト。設計中のコンピューターにおける、inc/dec 以外の演算を網羅している。

なお、m1, m2, m4 は、コマンドラインのデータ信号。

なお、m1, m2, m4 は、コマンドラインのデータ信号。

演算回路 [デジタル回路]

2007年6月27日

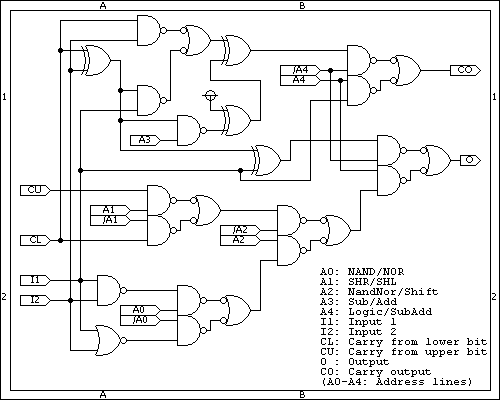

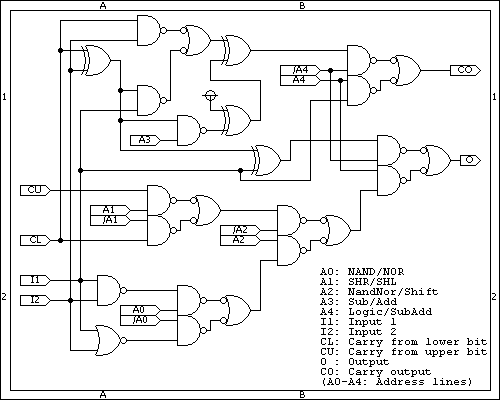

演算回路の設計図が完成。CPUの機能を少し変更することになりそう。a1/a2レジスタに、shiftとincrementの両方の機能を搭載すると回路が複雑になるため、shiftの演算結果はxレジスタに出力することにする。ここに書いた回路は、shift命令を含んでいる。

(追記:A0-A4はアドレスラインではなく、コマンドの0-4ビット目の間違い)

(追記:A0-A4はアドレスラインではなく、コマンドの0-4ビット目の間違い)

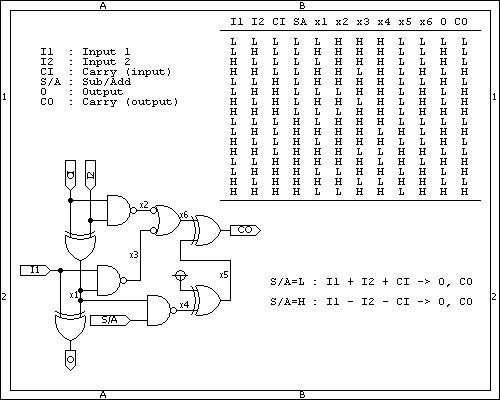

加算・減算回路 [デジタル回路]

2007年6月26日

AND, OR, XOR, NOT を用いて加算・減算回路を設計すると、次のようになった。なお、キャリーを無視した1ビットの加算と減算は、同じ答えになる(回路のOutput)。

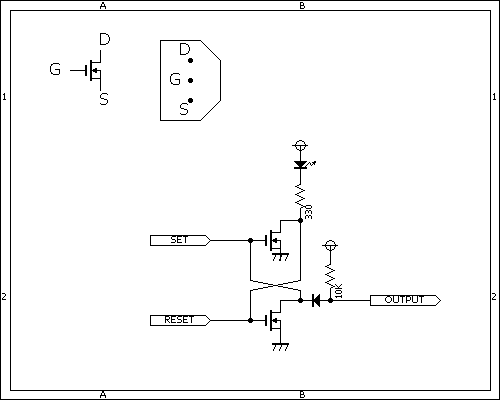

フリップフロップ [デジタル回路]

2007年4月25日

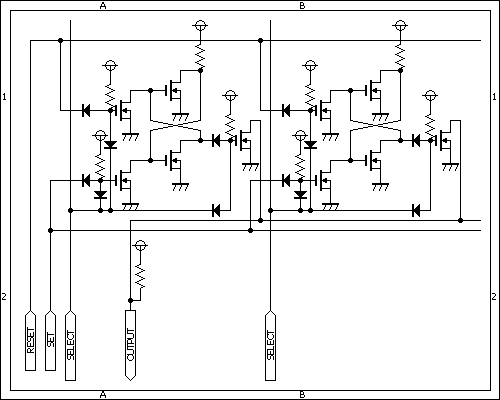

RAMの基本となる、記憶回路。記憶自体は2つのNANDで実現できるが、選択信号による接続・非接続の部分に3つのNANDが要りそう。再考の余地あり。

もしかしたらこの部分は、はじめからMOSFETで組んだ方が楽かもしれない。

一方で、ROMの方はダイオード一本で1ビット出来そうである。もしかしたら、ROMの容量を上げて、RAMの容量は必要最小限に抑えるかもしれない。