電子ブロック工房:2007年 06月の記事

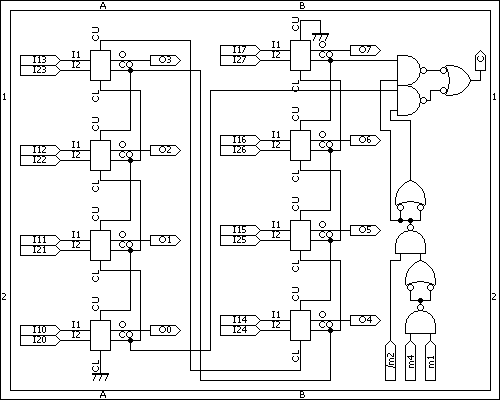

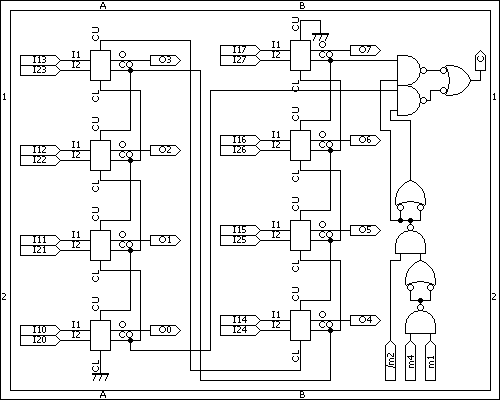

8ビット演算回路 [デジタル回路]

2007年6月29日

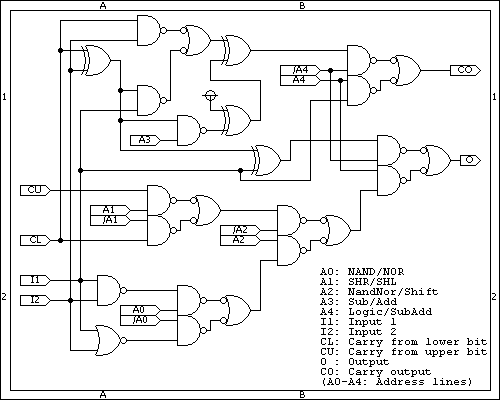

先日の回路を組み合わせて、8ビットどうしの演算をするための回路を設計した。実行できるのは、加算・減算・NAND・NOR・右シフト・左シフト。設計中のコンピューターにおける、inc/dec 以外の演算を網羅している。

なお、m1, m2, m4 は、コマンドラインのデータ信号。

なお、m1, m2, m4 は、コマンドラインのデータ信号。

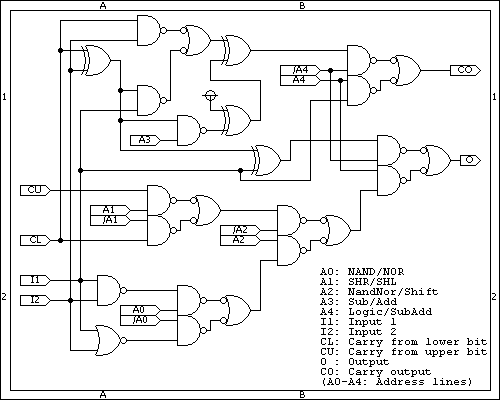

演算回路 [デジタル回路]

2007年6月27日

演算回路の設計図が完成。CPUの機能を少し変更することになりそう。a1/a2レジスタに、shiftとincrementの両方の機能を搭載すると回路が複雑になるため、shiftの演算結果はxレジスタに出力することにする。ここに書いた回路は、shift命令を含んでいる。

(追記:A0-A4はアドレスラインではなく、コマンドの0-4ビット目の間違い)

(追記:A0-A4はアドレスラインではなく、コマンドの0-4ビット目の間違い)

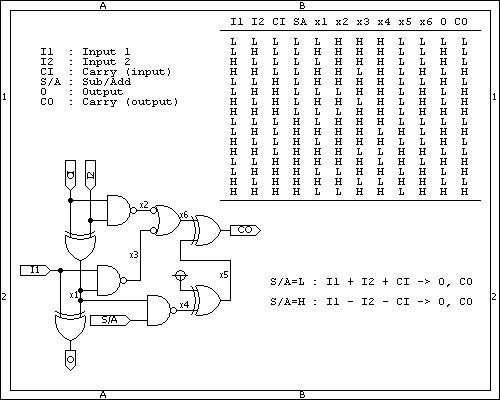

加算・減算回路 [デジタル回路]

2007年6月26日

AND, OR, XOR, NOT を用いて加算・減算回路を設計すると、次のようになった。なお、キャリーを無視した1ビットの加算と減算は、同じ答えになる(回路のOutput)。

ニーモニック表を更新 [CPU]

2007年6月24日

ニーモニック表を更新した。主な変更点:

1)複合命令を追加・更新した。

2)sub a2,a2 を廃止し、ここに mov x,[ip++] という、複合命令用の命令を割り当てた。これにより、複合命令を用いて、マルチバイトの命令を実行することが可能になった(mov a1,XXh など)。

1)複合命令を追加・更新した。

2)sub a2,a2 を廃止し、ここに mov x,[ip++] という、複合命令用の命令を割り当てた。これにより、複合命令を用いて、マルチバイトの命令を実行することが可能になった(mov a1,XXh など)。

シミュレータが完成 [シミュレーション]

2007年6月24日

シミュレータが、(おそらく)完成した。最後に残っていた、複合命令まわりのコードを仕上げた。いくつかの複合命令を実行してみたが、うまく動いている様子。

8ビットどうしの掛け算 [シミュレーション]

2007年6月23日

新しいニーモニック表を用いたマシン語で、8ビットどうしの掛け算を行なった。このルーチンを汎用サブルーチンとしてメモリに確保しておき、これを利用する形で16ビットどうしの掛け算を行わせる予定。

メモリアクセス機能を追加 [CPU]

2007年6月23日

ニーモニック表を更新。

1)[b1], [b2] へのアクセスだけでは無理がありそうなので、[b1+1], [b1+2], [b1+3], [b2-1], [b2-2], [b2-3] へも、x レジスタから読み書きできるようにした。従来の mov x,[b1] は、mov xl, [b1]l へと変更したので、selector 周りのコードも少しすっきりした。

2)push b2, push ss を廃止し、代わりに push x, push f とした。

他に、気のついたところ:

1)cmp 命令が欲しい。

2)sub a2,a2 は不要なので、ここに何かの命令を割り当てられそう(sub a1,a1 は、x レジスタの値をゼロにするのに有用)。

3)ローテート命令を複合命令として実装すれば、便利。

4)シフト命令は、shr a1 と shl a2 の二つにし、shr a2 と shl a1 は複合命令を用いて記述するようにするかもしれない。

5)複合命令用に、inc cs:ip, dec cs:ip があれば、便利かもしれない。

1)[b1], [b2] へのアクセスだけでは無理がありそうなので、[b1+1], [b1+2], [b1+3], [b2-1], [b2-2], [b2-3] へも、x レジスタから読み書きできるようにした。従来の mov x,[b1] は、mov xl, [b1]l へと変更したので、selector 周りのコードも少しすっきりした。

2)push b2, push ss を廃止し、代わりに push x, push f とした。

他に、気のついたところ:

1)cmp 命令が欲しい。

2)sub a2,a2 は不要なので、ここに何かの命令を割り当てられそう(sub a1,a1 は、x レジスタの値をゼロにするのに有用)。

3)ローテート命令を複合命令として実装すれば、便利。

4)シフト命令は、shr a1 と shl a2 の二つにし、shr a2 と shl a1 は複合命令を用いて記述するようにするかもしれない。

5)複合命令用に、inc cs:ip, dec cs:ip があれば、便利かもしれない。

シミュレータのデバッグと起動 [シミュレーション]

2007年6月18日

先日シミュレータの記事を書いた段階ではまだテストランもほとんど行っていなかったため、当然ながらバグだらけのコードであった。デバッグを行い、簡単なマシン語を実行してみた。