NMOSで作ったD-FF

2015年5月2日

コンピューターの原理を考える上で、フリップフロップ(FF)の理解は欠かせない。FFの安定動作は、CPU全体の安定動作に必須の条件だ。トランジスターでどの様に回路を組めば、FFが安定して動作するかを考察・実験してみた。

ほぼ出来上がっているトランジスターCPUの回路に於いて、FFはすべて、DタイプFFとして実装している。そこで、D-FFをブレッドボード上に構築して、予想したとおり動作するかどうかを、実験した。

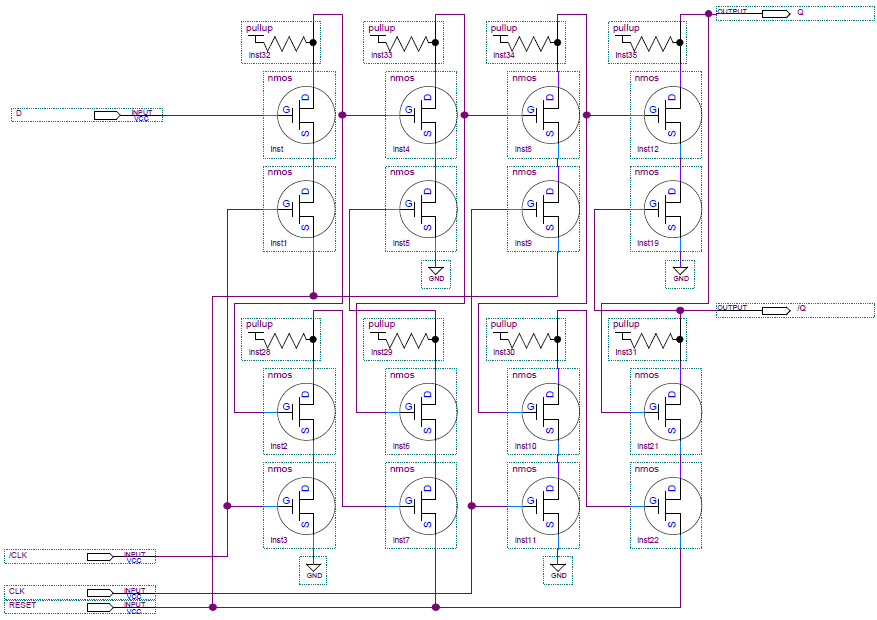

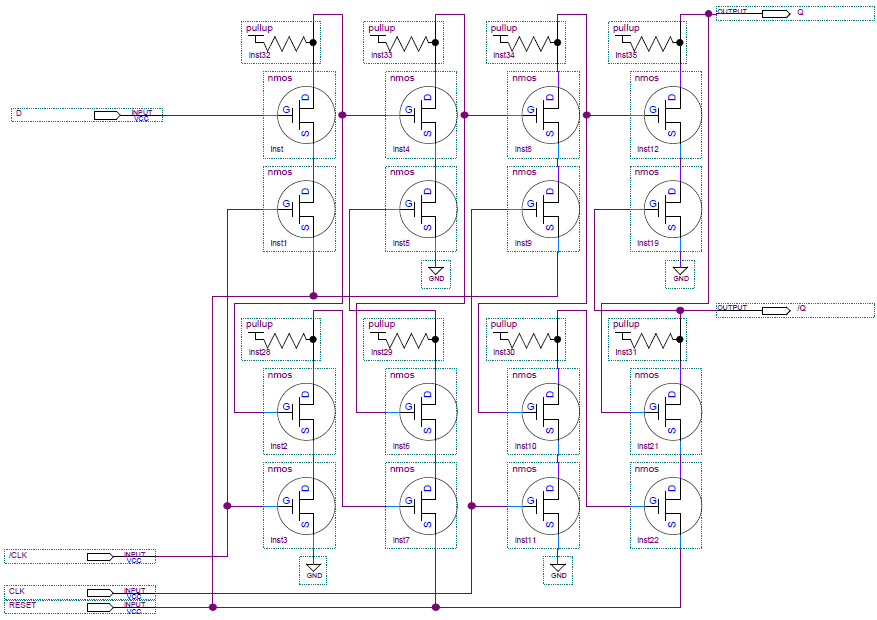

現在の所、D-FFはNMOSを用いて次の様に構築する予定である。

通常、D-FFのクロック入力は一つだけであるが、カウンターを構築する上で複数のFFが同一のクロックを用いるような構成になるため、回路の簡略化とFF同士の同期を考えて、CLKと/CLKの2つのクロック入力端子を設けてある。このFFは、2つのDタイプラッチがタンデムに接続された構成になっていて、CLKと/CLKはそれぞれ、スレーブラッチ(右側8個のNMOS)、マスターラッチ(左側8個のNMOS)に接続されている。

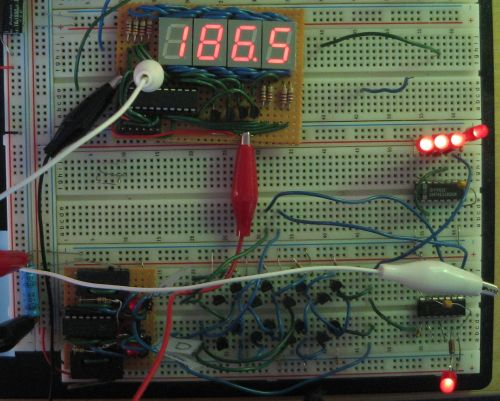

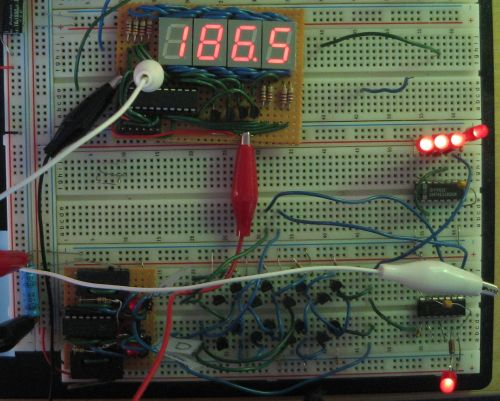

まずは、この回路が正常に動作するかを、ブレッドボードでテストしてみた。/QをDにつなぎ、T-FFの構成にして、入力されたシグナルの周波数が半分になるかどうかを、測定。まずは、入力周波数の測定。186.5 kHzの表示。

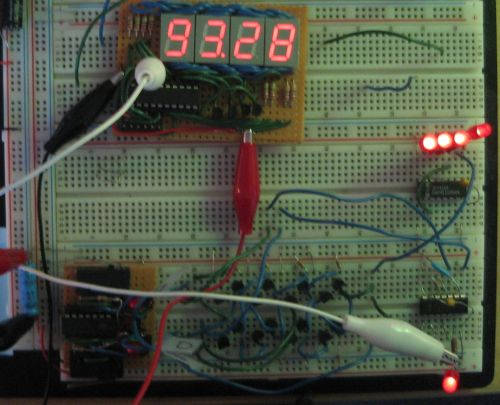

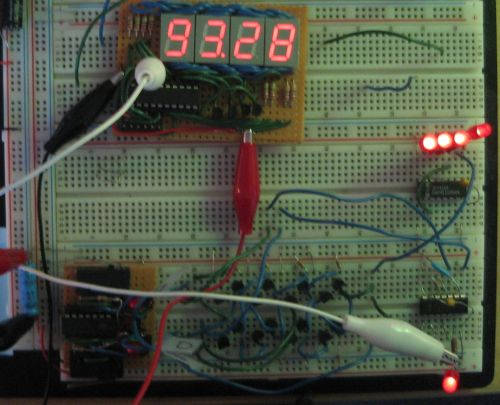

次に、MOSFET-Nトランジスターで構成したD-FFにこのシグナルを入れて、出力側の周波数を測定。

93.28 kHzの表示。ちゃんと、半分の周波数になっている。実験では、これぐらいの周波数が限界で、さらに速くすると、ちゃんと動作しなかった。トランジスターCPUの完成品では、50-100 kHzぐらいのクロックで動かすことになるだろう。

このテストでは、D-FFが10 kΩプルアップでのNMOSの構成であるのに対し、CLKと/CLKの入力部分にCMOSのNOTを用いている。従って、D-FF回路に比べると、CLK-/CLK作成回路は格段に速い動作をする。マスタースレーブ型のFFの動作を考える上で、CLK, /CLKの2つの入力が速い動作であるのは、理想的な回路構成である。しかし、設計しているCPU内では、すべての回路に10 kΩプルアップのNMOSを使用する予定なので、CLK, /CLKだけ高速動作というわけに行かない。CLKと/CLKの2つのシグナルが同時に変化していればよいが、少しズレがあるようなケースについて考えておく必要があるだろう。

CLKシグナル立ち上がりの際に/CLKシグナルの立ち下がりも同時に起これば、問題なく動作するはずであるが、このタイミングがずれてしまった場合について考える。もし、CLK=H, /CLK=Hの時間が一定以上長く続くと、2つのラッチが両方ともゲートが開いた状態になってしまい、誤作動の原因になる。他方で、CLK=L, /CLK=Lの時間があったとしても、FF誤作動の原因にはなり得ない。これは、CLKシグナル立ち下がりの際も、同様である。従って、CLK=H, /CLK=Hとなるようなことが決していないような設計にすればよいということになる。

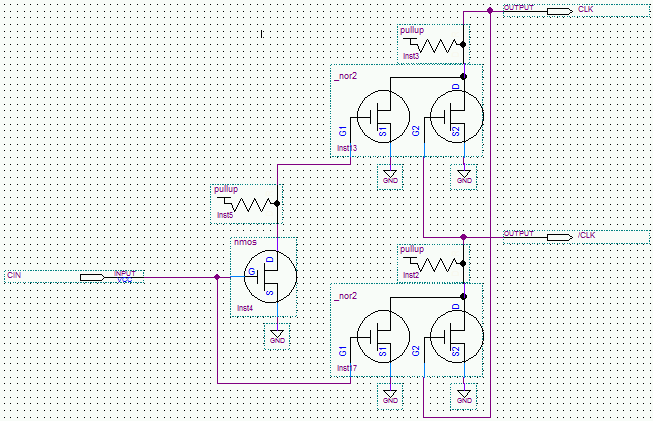

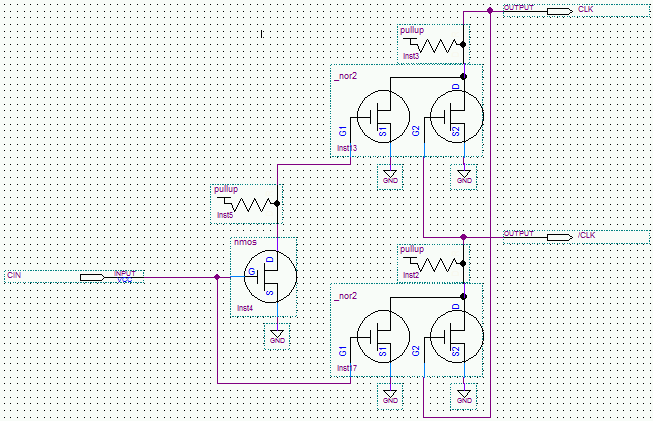

このようなCLK, /CLKの作成のために、次のような回路を挿入することにした。

この回路の動作を、Quartus II上でシミュレーションすると、以下のようになる。CLK立ち上がり、立ち下がり、いずれの場合においても、CLK, /CLKの両方がHになることはない。

シミュレーションだけではなく、ブレッドボード上のD-FFでも、このクロック作成回路が問題なく働くことを確認した。

FFのクロック部分についてはずいぶん悩んでいて、FFを作成する場合に、同じMOSFET-Nの同じロットを用いてthresholdをそろえておいて、安定動作を計ろうかなどと考えていた。それ用に、個々のMOSFETのthresholdを測定するための回路をPICで組んで、購入したMOSFETを調べたりしていた。しかし、上記のCLK-/CLK作成回路を使えば、少々thresholdのずれたMOSFETを混在させて回路を組んでも、誤作動する心配はなさそうである。

だいぶ煮詰まってきた。そろそろ、半田付けを始めたい。少しまとまった回路(ジョンソンカウンター)を作成して動作確認を行なった後に、CPU全体の回路を公表する予定。現在の所、CPUを構成するトランジスターの数は合計で651個である。

ほぼ出来上がっているトランジスターCPUの回路に於いて、FFはすべて、DタイプFFとして実装している。そこで、D-FFをブレッドボード上に構築して、予想したとおり動作するかどうかを、実験した。

現在の所、D-FFはNMOSを用いて次の様に構築する予定である。

通常、D-FFのクロック入力は一つだけであるが、カウンターを構築する上で複数のFFが同一のクロックを用いるような構成になるため、回路の簡略化とFF同士の同期を考えて、CLKと/CLKの2つのクロック入力端子を設けてある。このFFは、2つのDタイプラッチがタンデムに接続された構成になっていて、CLKと/CLKはそれぞれ、スレーブラッチ(右側8個のNMOS)、マスターラッチ(左側8個のNMOS)に接続されている。

まずは、この回路が正常に動作するかを、ブレッドボードでテストしてみた。/QをDにつなぎ、T-FFの構成にして、入力されたシグナルの周波数が半分になるかどうかを、測定。まずは、入力周波数の測定。186.5 kHzの表示。

次に、MOSFET-Nトランジスターで構成したD-FFにこのシグナルを入れて、出力側の周波数を測定。

93.28 kHzの表示。ちゃんと、半分の周波数になっている。実験では、これぐらいの周波数が限界で、さらに速くすると、ちゃんと動作しなかった。トランジスターCPUの完成品では、50-100 kHzぐらいのクロックで動かすことになるだろう。

このテストでは、D-FFが10 kΩプルアップでのNMOSの構成であるのに対し、CLKと/CLKの入力部分にCMOSのNOTを用いている。従って、D-FF回路に比べると、CLK-/CLK作成回路は格段に速い動作をする。マスタースレーブ型のFFの動作を考える上で、CLK, /CLKの2つの入力が速い動作であるのは、理想的な回路構成である。しかし、設計しているCPU内では、すべての回路に10 kΩプルアップのNMOSを使用する予定なので、CLK, /CLKだけ高速動作というわけに行かない。CLKと/CLKの2つのシグナルが同時に変化していればよいが、少しズレがあるようなケースについて考えておく必要があるだろう。

CLKシグナル立ち上がりの際に/CLKシグナルの立ち下がりも同時に起これば、問題なく動作するはずであるが、このタイミングがずれてしまった場合について考える。もし、CLK=H, /CLK=Hの時間が一定以上長く続くと、2つのラッチが両方ともゲートが開いた状態になってしまい、誤作動の原因になる。他方で、CLK=L, /CLK=Lの時間があったとしても、FF誤作動の原因にはなり得ない。これは、CLKシグナル立ち下がりの際も、同様である。従って、CLK=H, /CLK=Hとなるようなことが決していないような設計にすればよいということになる。

このようなCLK, /CLKの作成のために、次のような回路を挿入することにした。

この回路の動作を、Quartus II上でシミュレーションすると、以下のようになる。CLK立ち上がり、立ち下がり、いずれの場合においても、CLK, /CLKの両方がHになることはない。

シミュレーションだけではなく、ブレッドボード上のD-FFでも、このクロック作成回路が問題なく働くことを確認した。

FFのクロック部分についてはずいぶん悩んでいて、FFを作成する場合に、同じMOSFET-Nの同じロットを用いてthresholdをそろえておいて、安定動作を計ろうかなどと考えていた。それ用に、個々のMOSFETのthresholdを測定するための回路をPICで組んで、購入したMOSFETを調べたりしていた。しかし、上記のCLK-/CLK作成回路を使えば、少々thresholdのずれたMOSFETを混在させて回路を組んでも、誤作動する心配はなさそうである。

だいぶ煮詰まってきた。そろそろ、半田付けを始めたい。少しまとまった回路(ジョンソンカウンター)を作成して動作確認を行なった後に、CPU全体の回路を公表する予定。現在の所、CPUを構成するトランジスターの数は合計で651個である。